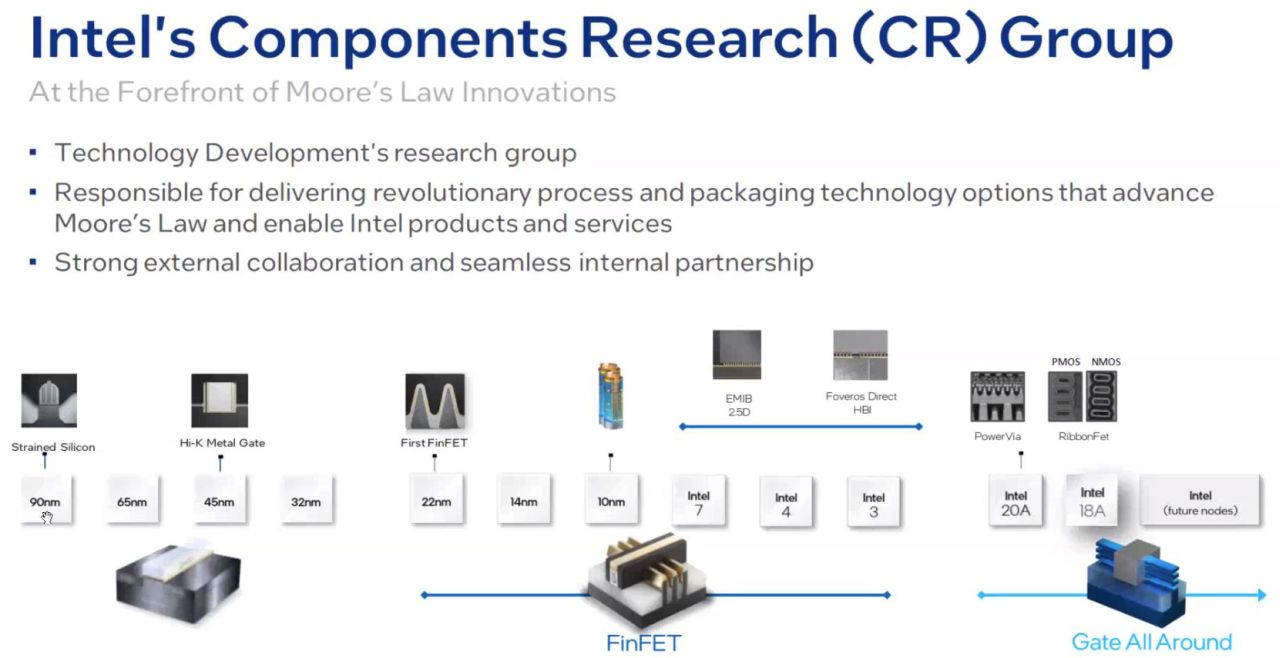

Intel ha presentato una serie di innovazioni tecnologiche nei transistor per la tabella di marcia dei processi futuri, novità che secondo il produttore permetteranno di riaffermare la prosecuzione e l’evoluzione della Legge di Moore.

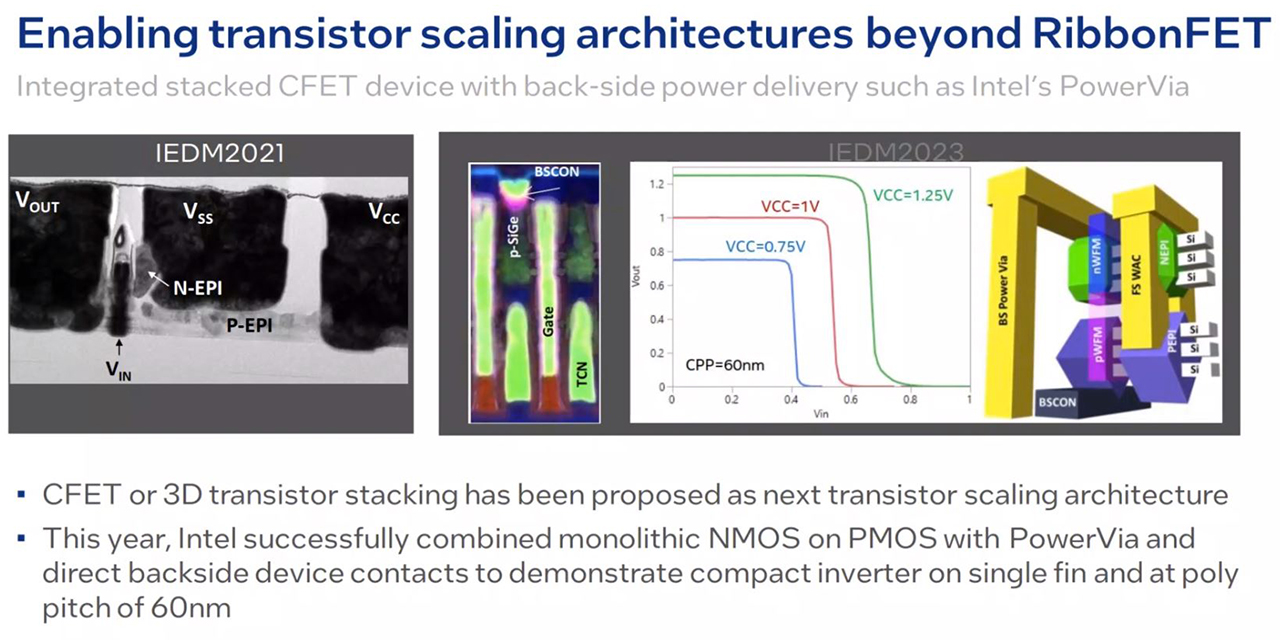

In occasione dell’IEEE International Electron Devices Meeting (IEDM) 2023, i ricercatori di Intel hanno presentato avanzamenti nei transistor CMOS (Complementary Metal Oxide Semiconductor) con stack 3D uniti ad alimentazione e contatti diretti dal retro.

L’azienda ha inoltre presentato (qui i dettagli) aggiornamenti sui percorsi di scalabilità con novità che riguardano l’erogazione di energia dal retro, inclusi i contatti posteriori, ed ha mostrato l’integrazione monolitica 3D su larga scala di transistor in silicio con transistor in nitruro di gallio (GaN) sugli stessi wafer da 300 mm, anziché sul package.

Intel spiega che la scalabilità dei transistor e l’alimentazione dal retro sono fondamentali per contribuire a soddisfare la crescente domanda di computer sempre più potenti. Il gruppo di ricerca sui componenti spinge i confini della progettazione con i transistor stacked, portando l’alimentazione dal retro a un livello superiore per consentire una maggiore scalabilità dei transistor e migliori prestazioni, dimostrando che transistor realizzati con materiali diversi possono essere integrati sullo stesso wafer.

I ricercatori hanno identificato le principali aree di ricerca e sviluppo necessarie per continuare a crescere lavorando sull’efficienza dello stacking dei transistor. Combinati con l’alimentazione e i contatti dal retro rappresenteranno importanti passi avanti nell’architettura dei transistor.

Oltre a migliorare l’erogazione di potenza dal retro e a utilizzare nuovi materiali per canali 2D, Intel sta lavorando per estendere la legge di Moore a mille miliardi (one trillion) di transistor su un pacchetto entro il 2030.

La capacità di impilare verticalmente transistor a effetto di campo complementare (CFET) con un passo di gate ridotto fino a 60 nanometri, secondo il produttore offre vantaggi in termini di efficienza dell’area e maggiori prestazioni grazie allo stacking dei transistor.

Altra innovazione mostrata quest’anno riguarda progressi fatti nell’integrazione dei processi di silicio e GaN con una soluzione denominata “DrGaN”, per l’erogazione di energia.

Intel riferisce ancora che i materiali per canali 2D Transition Metal Dichalcogenide (TMD) offrono un’opportunità unica per la lunghezza del gate fisico dei transistor su scala inferiore a 10 nm.

L’azienda presenterà prototipi di transistor TMD ad alta mobilità sia per NMOS (N-channel Metal Oxide Semiconductor) che PMOS (P-channel Metal Oxide Semiconductor), i componenti chiave del CMOS. Intel presenterà inoltre il primo transistor PMOS TMD 2D gate-all-around (GAA) al mondo e il primo transistor 2D PMOS al mondo fabbricato su un wafer da 300 mm.

Insieme a IBM, Meta, Nasa e oltre 40 società Intel collabora per lo sviluppo di intelligenza artificiale open source.